# NANOELECTRONICS: <u>APPLICATIONS</u> AND ARCHITECTURES

**NRI-NRC Future Architectures Workshop- University of Notre Dame**

#### 18 August 2009

Larry Cooper Adjunct Faculty-Arizona State University

Office of Naval Research (ret.)

**ONR Program Officer-Nanoelectronics (1973-2003)**

# THE NAVY APPROACH

# TO OBSERVE BUT <u>NOT COMPETE</u> WITH COMMERCIAL INDUSTRIES FOLLOWING-

### "THE "ROAD MAP"

## TO EXPLORE DIFFERENT <u>MATERIALS</u>, DIFFERENT <u>DEVICES</u> AND DIFFERENT <u>ARCHITECTURES</u> IN ORDER TO:

## PROVIDE ADVANCED MILITARY SYSTEMS WITH CAPABILITIES IN COMPUTATIONAL <u>SPEED</u>, REDUCED ELECTRICAL <u>POWER</u> AND REDUCED COMPONENT <u>VOLUME</u>

## **BRIEF HISTORY**

### "The Navy Nanoelectronics Program"

<u>1973- New Program Area</u>

**Radiation Effects in semiconductor devices**

Contacts and interfaces between dissimilar materials

Shrinking silicon devices

=>Physics based modeling of semiconductor devices

#### 1977- Major and Focused Program to Support Nanoelectronics Research

<u>USER-U</u>Itra <u>Submicron Electronics Research</u>

(NERD-<u>N</u>ano <u>E</u>lectronics <u>R</u>esearch for <u>D</u>efense)

<u>1997- ONR Grand Challenge program for Navy impact in 30-50 years</u> Multifunctional Electronics for Intelligent Naval Sensors

# <u>1977-USER</u>

"Develop a long term basic research program leading to the development of electronics technology based on devices with 20 Angstrom dimensions" (2 Nanometers)

#### Major Components

>Materials (thin film)

Silicon

**Compound semiconductors**

**Ferromagnetic films**

**>Fabrication Technologies**

**Electron Beam**

Ion Beam

Patterned self-assembly

>Device Physics

**Electronic-Magnetic-Optical**

Nano- 3D, 2D, 1D, "0D"

**Physics based device simulations**

>Computing Architectures

**Local interconnects**

Parallel processing

**3 Dimensional Integration**

# 1997-ONR GRAND CHALLENGE "<u>Multifunctional Electronics for Intelligent</u> <u>Naval Sensors"</u>

Research Programs To Impact on the Navy in 30 to 50 Years!

To develop highly multifunctional nanoscale devices to their **ultimate limits** of higher speed <u>(1000x)</u>, lower power <u>(0.001x)</u>, and smaller volume <u>(0.001x)</u> (SPV) and for systems that interactively combine sensing, image processing, computation, signal processing, and communications functions to achieve real-time adaptive response for Navy missions.

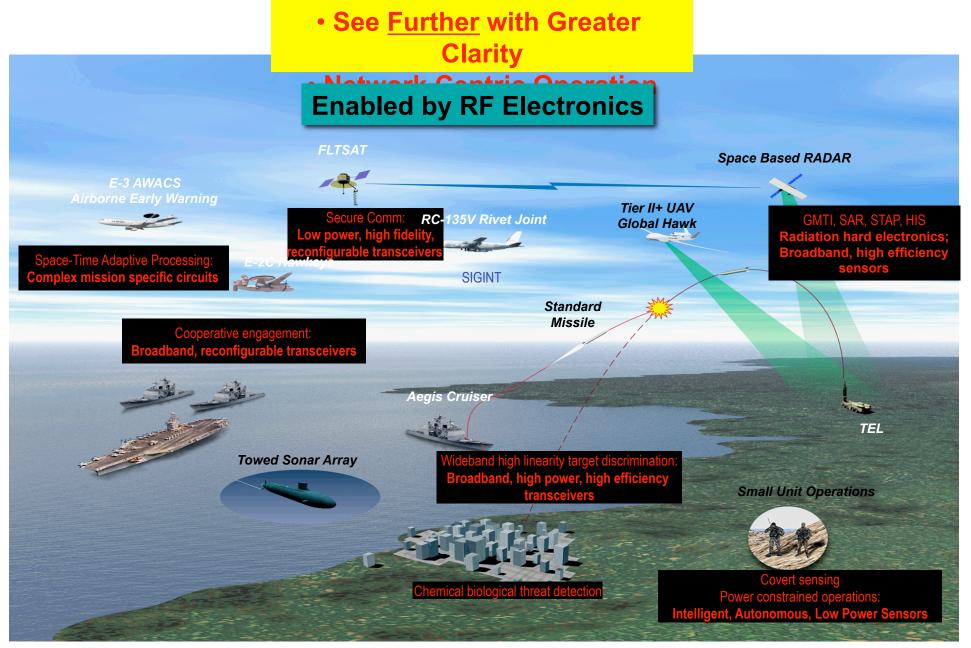

## NANOELECTRONICS IS THE KEY ENABLER

### Asymmetric Advantage Enabled by *Information Superiority*

# **FUTURE NAVAL CAPABILITIES**

- Nanoelectronics will be a critical factor for FNCs

- AUTONOMOUS OPERATIONS

- SENSOR DATA PROCESSING

- INTELLIGENT\_AUTONOMY

- ELECTRIC SHIPS

- INTELLIGENT SENSORS

- KNOWLEDGE SUPERIORITY & ASSURANCE

- IMAGE PROCESSING

- INFORMATION MANAGEMENT

- MISSILE DEFENSE

- SMART WEAPONS SENSORS

- PLATFORM PROTECTION

- SMART WEAPONS SENSORS

- DISTRIBUTED SENSORS

- TIME CRITICAL STRIKE

- DISTRIBUTED SMART SENSORS

- IMAGE & VIDEO ANALYSIS

- WARFIGHTER PROTECTION

- SIGNIFICANTLY ENHANCED SITUATION AWARENESS

(automatic response)

### "Finding the Right Device for the Application" NANOELECTRONIC DEVICES

#### <u>NOW</u>

SILICON TRANSISTORSHETEROJUNCTION DEVICESNANOMAGNETIC DEVICESRESONANT TUNNELING DEVICESPROGRAMMABLE METALLIZATION CELL MEMORY (PMC)

#### <u>NEXT?</u>

SINGLE ELECTRON DEVICESNANOMAGNETS FOR MQCASPINTRONIC DEVICESCARBON NANOTUBESSPIN TORQUE MEMORY (DARPA)SCHOTTKY GATE SUBTHRESHOLD TRANSISTORS

#### NEVER?

| MOLECULAR TRANSISTORS          | GRAPHENE TRANSISTORS     |

|--------------------------------|--------------------------|

| NANOWIRE TRANSISTORS           | DOMAIN WALL MEMORY/LOGIC |

| RESONANT TUNNELING TRANSISTORS | NANO MEMRISTOR           |

| MAGNETIC RTD                   | NANO MEMINDUCTOR         |

| QUANTUM COHERENT TRANSISTORS   | NANO MEMCAPACITOR        |

### **INFLUENCING/DOMINATING FACTORS**

**<u>SPEED</u>**-Terahertz Digital Signal Processing

**AMRFS-Advanced Multifunctional RF Systems**

**<u>POWER</u>**-Non-Volatile Reprogrammable Computing

Legacy electronics

Hybernating or "instant-turn-on-computing"

Low dissipation power

**VOLUME**-High performance hybrid integrated systems (SoC)

Surveillance

Targeting and tracking

**Bio-inspired Neuro-Computing**

# **SPEED**

**Compound Semiconductors**

**High Mobility**

Low voltage

Flexibility in hybrid systems

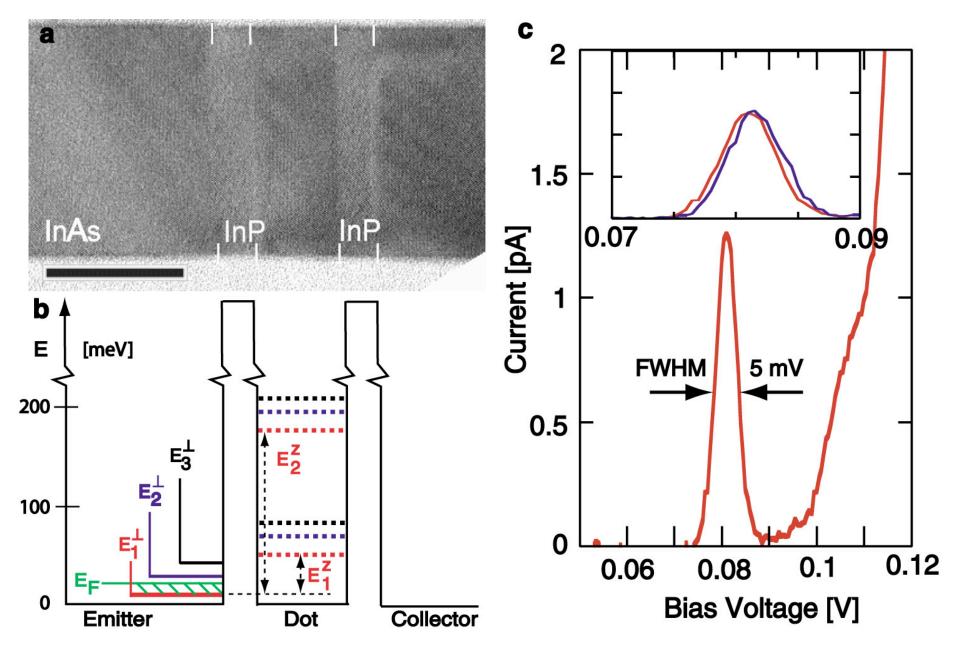

6.1 Angstrom- InAs/AISb/GaSb (Lattice matched)

InGaAs/InP

GaAs/GaAlAs

HFETs

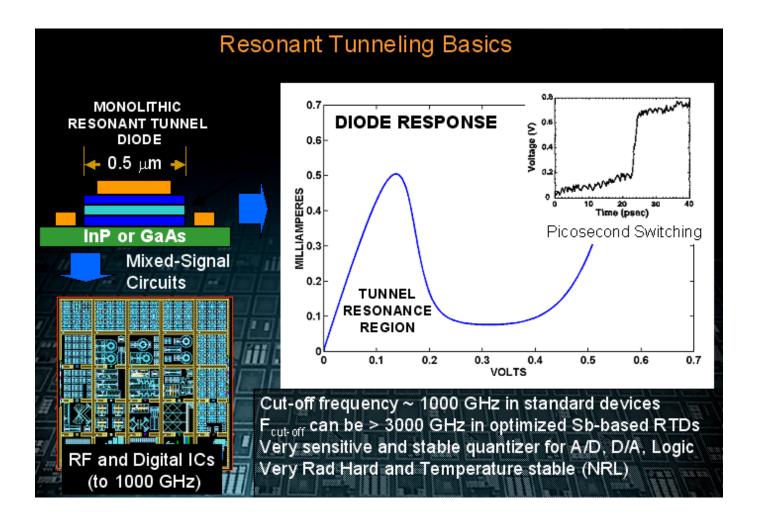

**Resonant Tunneling Diodes [f(T) > 3 THz]**

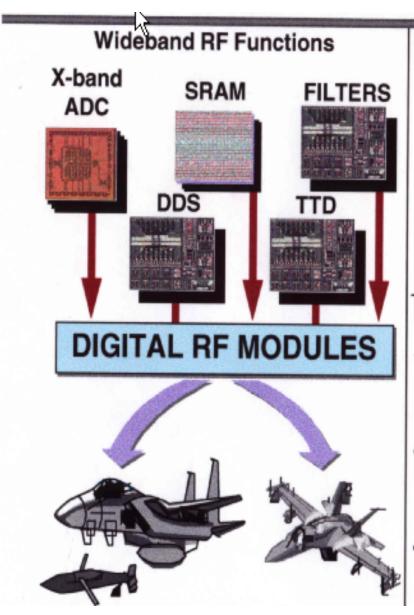

#### Advanced Multifunction RF-Concept (AMRF-C)-Cellular Antenna Arrays

Wideband (10-100 GigaHertz) *Digital* Antennae for Digital Beam Forming

Radar

Communications

**Electronic Warfare**

SAR-Synthetic Aperture Radar

(Colleague question-can we make 400 GigaHertz DSPs?)

### PROJECT OBJECTIVE:

Provide 10-100 GHz mixed signal components for advanced digital RF systems

### • FEATURES:

- Production InP IC Process

- Resonant Tunneling Devices

- FET/HBT Compatibility

### DoD BENEFITS:

- Component base for wideband digital RF Systems - Radar, SAR, Comm, RWR, EW

- 10-100 GHz ADC / DAC / DDS / Logic

- 4-10 GHz Digital IF

- Digital X-band Phased Arrays

- 1000X Lower power microwave SRAM

- True Time Delay / FIFOs / Buffers

First implementation of a 1D heterostructure nanoelectronic device in as a double-barrier resonant tunneling diode (DBRTD) in InAs with InP k

# **POWER**

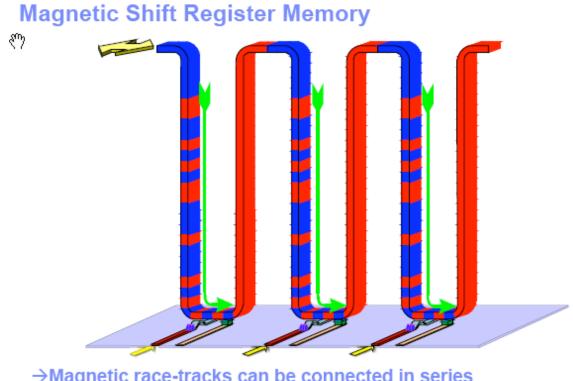

Nano Magnetics

Non-volatile Memory/Logic

**Dilute magnetic semiconductors (Spintronics)**

Hybrid magnetic/semiconductor (magnetic state variable?)

High mobility semiconductors (HFETs and RTDs)

Low voltage

**High Speed**

Fewer devices per function

Non-volatile Memory

# NON-VOLATILE

#### **ELECTRONICS**

#### **Nano-magnetics**

**Programmable/Reprogrammable Logic**

**Universal Circuits (?)**

**Battery life**

**Radiation Hard**

**Legacy Electronics**

Instant-turn-on-computer

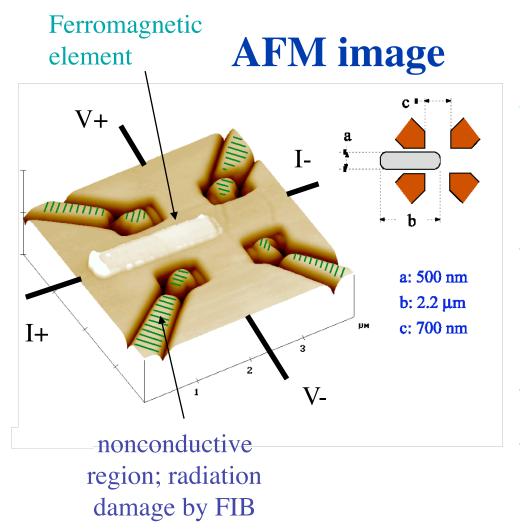

# Magnetoelectronic Reprogrammable Logic

- New paradigm for **Programmable** (and **Reprogrammable**) **Logic**

- Reduce dependence on ASIC components.

- Low cost, multifunctional alternative:

- Reprogram by software (data input stream) hardware upgrade (reprogram chip function) can be achieved by software; fast and inexpensive; test and reprogram to achieve self-healing circuits

- Rad hard; multi-GHz operation

- Dual-use applications, such as satellite (and other space based systems), missile guidance units, consumer electronics, etc.

- Inexpensive alternative: Field Programmable Gate Arrays (FPGA)

- Single design: array of identical blocks, each with "programmable" function

# HHE-Hybrid Hall Effect Device (Research Prototype-sub-micron)

- Demonstrate scaling to f = 500 nm

- Single F layer 500 nm by 2.2 [\*]m, 55 nm thick Ni<sub>0.8</sub>Fe<sub>0.2</sub>

- mobility of S: 4500

- 30 mV output level

$\rightarrow$  Magnetic race-tracks can be connected in series  $\rightarrow$  Many other configurations possible

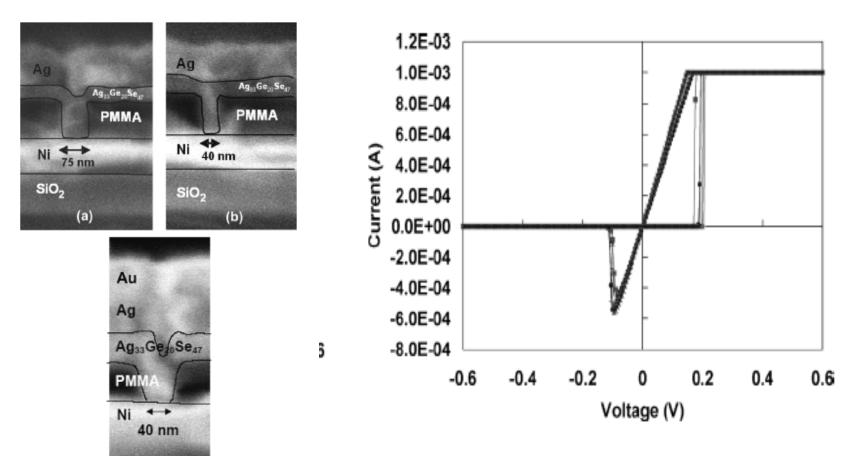

#### **NON-VOLATILE PROGRAMMABLE METALLIZATION CELL (PMC)**

Si0<sub>2</sub> (c)

Fig. 4. Current–voltage plot from a 40-nm structure fabricated using process B obtained using six voltage sweeps of -0.6 to +0.6 to -0.6 V with a 1-mA current limit. The device switches from over  $10^7 \Omega$  to its low resistance state of  $100 \Omega$  around 0.2 V and the conducting pathway breaks at -0.1 V.

# Programmable Metallization Cell Memory Performance Summary

- Low voltage

- Low current

- Low power

- High speed

- Low energy

- High retention

- High endurance

- High off/on ratio

- Good scalability

- Analog R<sub>on</sub>

- MLC capability

- High density

- Integrable

- Low cost

- **(0.5 V**

- 🕅 typ. 10 🕅 A (to 10 nA)

- ₩ W (to nW)

- Sector 20 ns write/erase/access

- **pJ** to fJ operation

- ▼ >10 years at elevated T

- $\times$  >>10<sup>12</sup> cycles

- **₩** >10<sup>5</sup>

- **10 nm**

- G is to tens of is programmable

- X 2 bits per cell shown, >2 possible

- Tb/chip possible at 22 nm with MLC

- I mask over logic, <u>BEOL compliant</u>

- **DRAM-like projections**

# VOLUME

**Digital functions**

**Analog functions**

Embedded memory

**3 Dimensional integration**

# NANO-ARCHITECTURES?

**CROSS-BAR**

CMOL

QCA/MQCA (field coupled devices)

**MOLECULAR** (directed self-assembly)

**PIP (Propagated Instruction Processor)**

**3 DIMENSIONALLY INTERCONNECTED PROCESSORS**

**NEURO-INSPIRED**

CELLULAR AUTOMATA

SPIN BASED RECONFIGURABLE LOGIC

**ARTIFICIAL NEURAL NETWORKS**

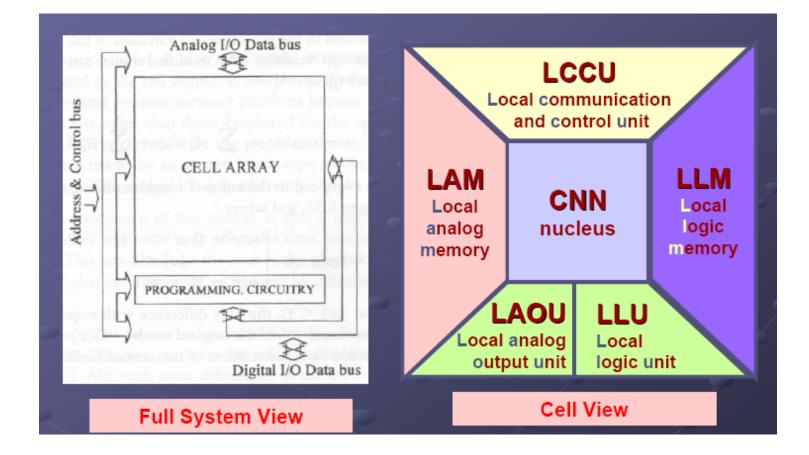

**CELLULAR NONLINEAR NETWORKS/CELLULAR NEURAL NETWORKS**

**<u>"CNN-UNIVERSAL MACHINE"</u>**

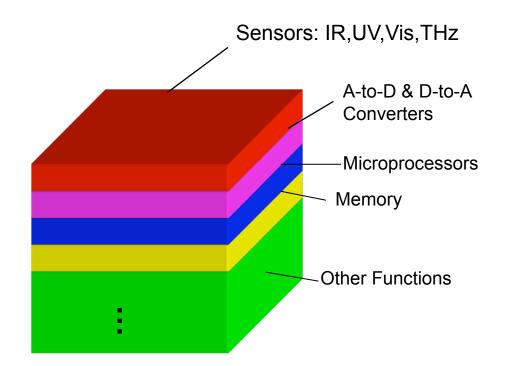

#### <u>1998-GRAND CHALLENGE</u> <u>"Multifunctional Electronics for Intelligent Naval Sensors"</u>

(To impact on the Navy in 30-50 years!)

Three-dimensional, ultra-dense, stacks of layers, each with a different function, ranging from sensors, to analog-to-digital converters, microprocessors, and memories.

Devices in each layer featuring sub-10 nm dimensions and lowpower-consumption, and often operating on non-classical phenomena such as quantum, or spin, or single-electron effects.

Layers intelligently connected with each other i.e. vias or nanowires.

**Other Functions:**

- adaptive control

- optical communication

- energy harvesting

Speed-1000X Power-1000X Volume-1000X

## SOLUTION

### **CNN-UNIVERSAL MACHINE**

LOCAL INTERCONNECTS

PARALLEL COMPUTING

NO CLOCK SKEW PROBLEMS

NO WIRE DELAY PROBLEMS

NO WIRE-TO-WIRE COUPLING

ANALOG OR DIGITAL DEVICES

**PROGRAMMABLE FUNCTIONS**

**INTEGRATED MEMORY**

**MULTIFUNCTION INTEGRATION**

MULTIPLE LAYERS (INTERCONNECTED)

### **NANOSCALE?**

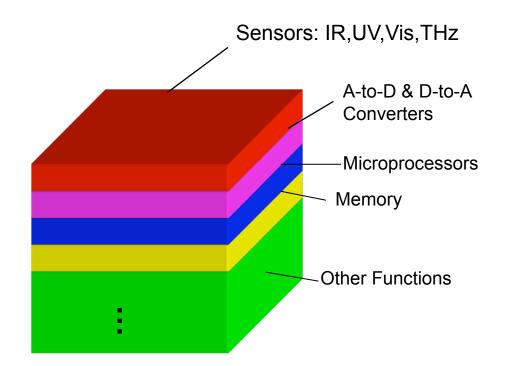

#### <u>1998-GRAND CHALLENGE</u> <u>"Multifunctional Electronics for Intelligent Naval Sensors"</u>

(To impact on the Navy in 30-50 years!)

Three-dimensional, ultra-dense, stacks of layers, each with a different function, ranging from sensors, to analog-to-digital converters, microprocessors, and memories.

Devices in each layer featuring sub-10 nm dimensions and lowpower-consumption, and often operating on non-classical phenomena such as quantum, or spin, or single-electron effects.

Layers intelligently connected with each other i.e. vias or nanowires.

**Other Functions:**

- adaptive control

- optical communication

- energy harvesting

Speed-1000X Power-1000X Volume-1000X

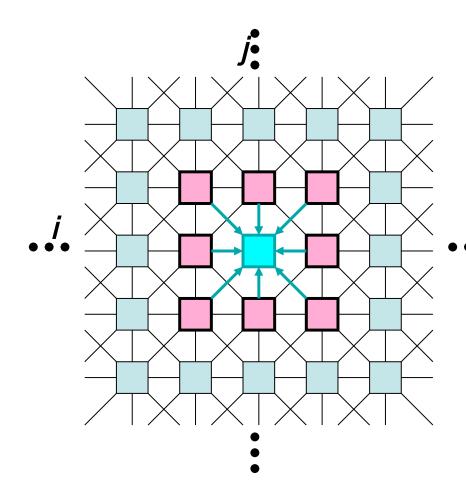

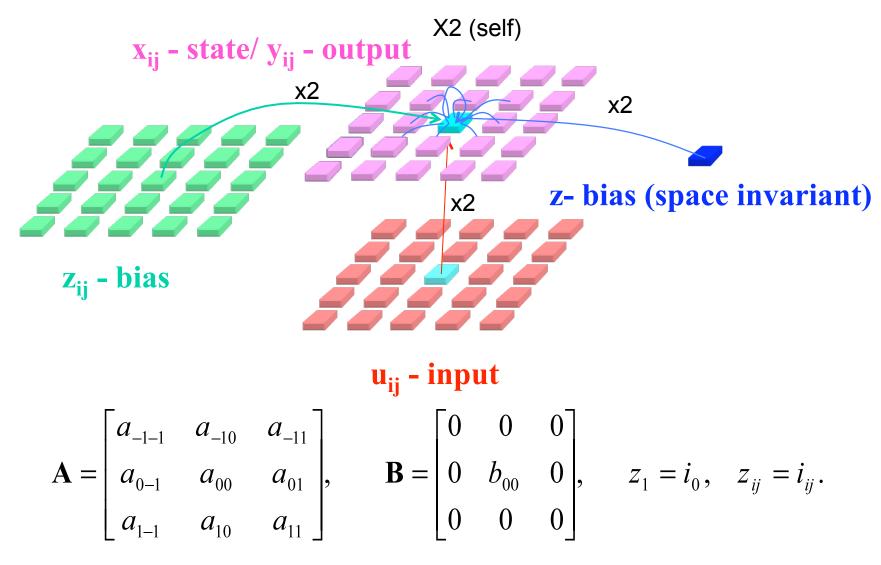

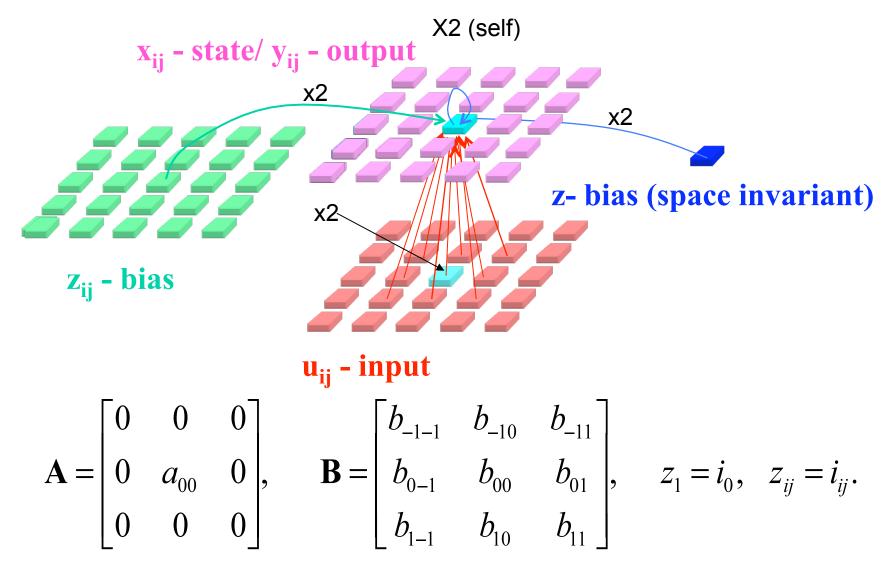

# **Introduction to CNN Dynamics**

The Cellular Nonlinear/Neural Network (CNN) is:

- an <u>analog</u> processor array

- on a 2D grid

- with mainly local interactions.

## **Template configurations I: Spatial feedback**

# **Template configurations II: Spatial feed-forward**

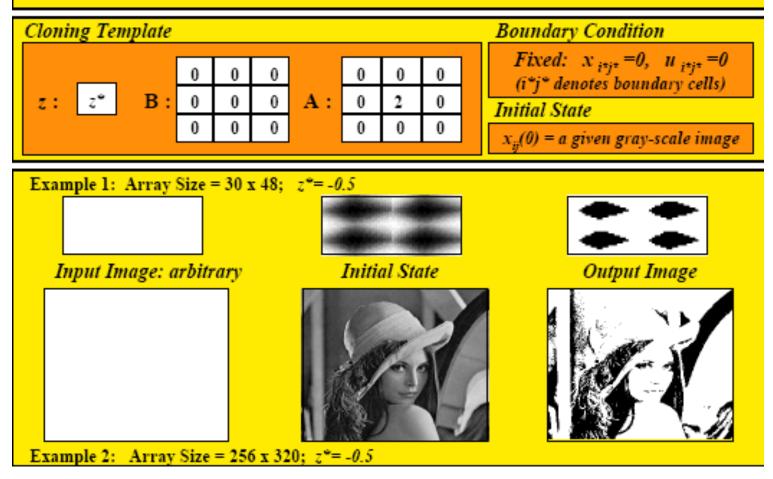

#### Name:

#### THRESHOLD CNN

Convert a gray-scale image P (loaded as initial state) into a binary image where each pixelTask $p_{ij} \in P$  is converted into "black" ("red" in pseudo-color) if, and only if,  $p_{ij}$  has a gray scale intensityPrescription:exceeding a prescribed value equal to the CNN threshold  $z^*$ . In the two extreme cases when  $z^*=1$ and  $z^*=-1$  all output pixels will be printed in black (red), or in white (blue) respectively.

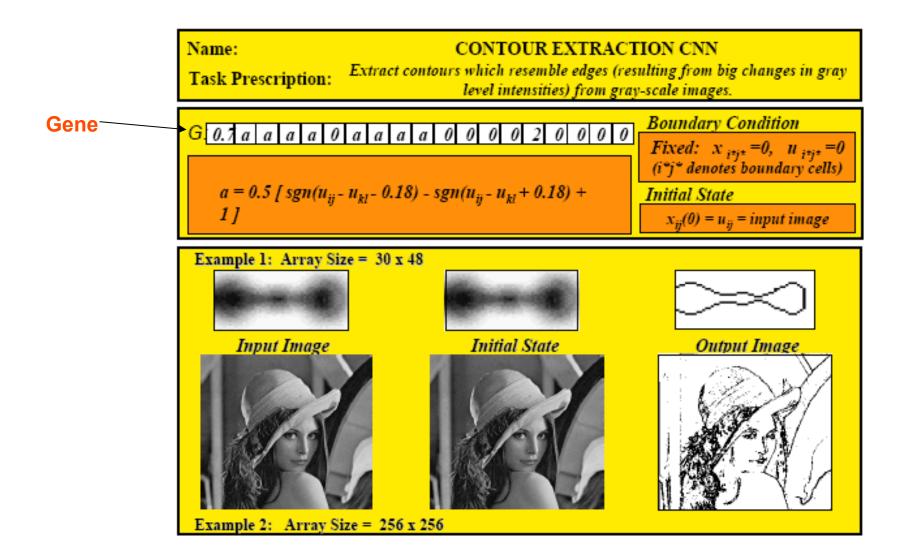

# SAMPLES OF CNN TEMPLATES (GENES)

**CONTOUR EXTRACTION**

**CORNER DETECTION**

HORIZONTAL TRANSLATION

VERTICAL TRANSLATION

**DIAGONAL TRANSLATION**

**POINT EXTRACTION**

THRESHOLDING

DEBLURRING

EROSION HALF TONING

**GRADIENT DETECTION**

**MANY MORE**

Image processing or pattern recognition involves using the programming language to run an algorithm using one or more of the templates. One template run can take 1 microsecond.

#### INTEGRATE DETECTOR WITHIN THE CELL OR THROUGH BUS CONNECTIONS

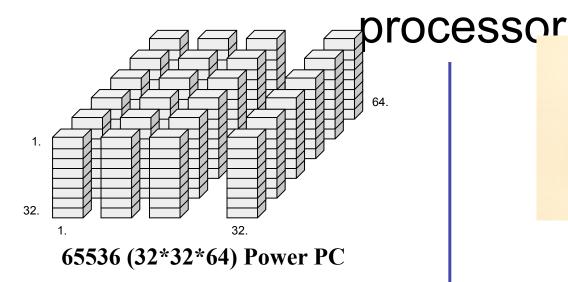

# Comparison between an IBM Cellular Supercomputer and an analogic

*IBM Cellular Supercomputer 2002* Computing Power ~ 12 \* 10<sup>12</sup> (TeraFLOPS)

$A = 65536 \text{ x} 1.06 \text{ cm}^2 = 6.9468 \text{ m}^2$

P = 491 kW

128 x 128 processor with optical input

An analog-and-logic CNN supercomputer

Computing Power ~ 12 \* 10<sup>12</sup> (**TeraOPS**) equivalent

$A = 1.4 \text{ cm}^2$

$$P = 4.5 W$$

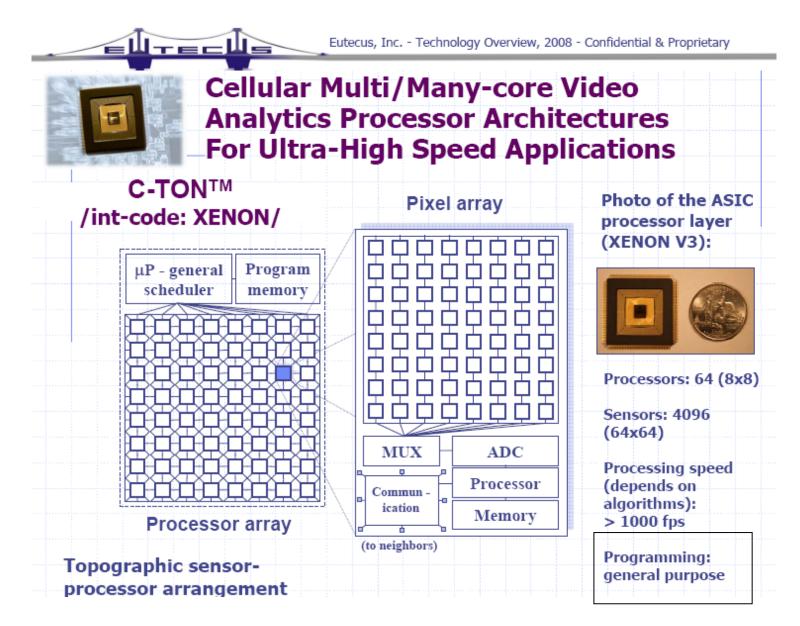

# UNIQUE FEATURES OF CNN-UM IMAGE PROCESSING

#### FULLY PROGRAMMABLE IMAGE PROCESSING COMPUTER ON A SINGLE CHIP

POWER DISSIPATION ORDERS OF MAGNITUDE SMALLER THAN WITH DIGITAL PROCESSORS

INTEGRATES PHOTODETECTOR SIGNALS DIRECTLY ONTO PROCESSOR CELLS

HIGH LEVEL PROGRAMMING LANGUAGE FOR ADAPTING TO ANY DESIRED IMAGE PROCESSING ALGORITHM

IMAGE INPUTS CAN BE DIGITAL OR ANALOG (ON-CHIP ADC AND DAC)

HIGH FRAME RATES SIGNIFICANTLY LARGER THAN DIGITAL PROCESSING

CELL FUNCTION IS EITHER ANALOG OR DIGITAL

45 nanometer silicon technology

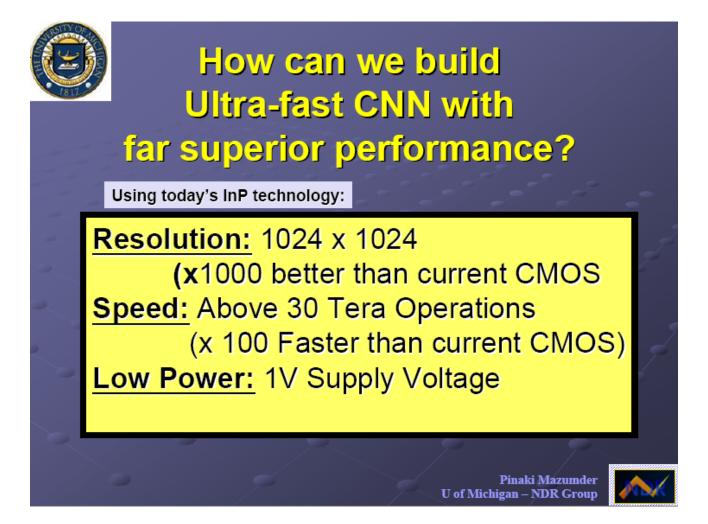

#### **RTD BASED CNN CIRCUIT SIMULATION (2003)**

Pinaki Mazumder (U Michigan)

## SAMPLE LIST OF APPLICATIONS:

AUTOMATIC TARGET RECOGNITION – ATR

UAV & MAV FOR SURVEILLANCE (BORDER?)

AUTONOMOUS VEHICLE NAVIGATION WALKING/CLIMBING ROBOTS

MULTIPLE TARGETS (TARGETING AND TRACKING)

MONITORING STREAMING VIDEO DATA (ON-SITE PROCESSING)

FACIAL RECOGNITION

HYPER-SPECTRAL SURVEILLANCE AND INTRUDER IDENTIFICATION

**COLLISION AVOIDANCE**

TRAFFIC CONTROL CAMERAS (!)

TACTILE SENSORS FOR ROBOTS (3 Dimensional)

SOUND LOCATOR

TOYS/GAMES

NEURO INSPIRED COMPUTING-"ARTIFICIAL EYE"

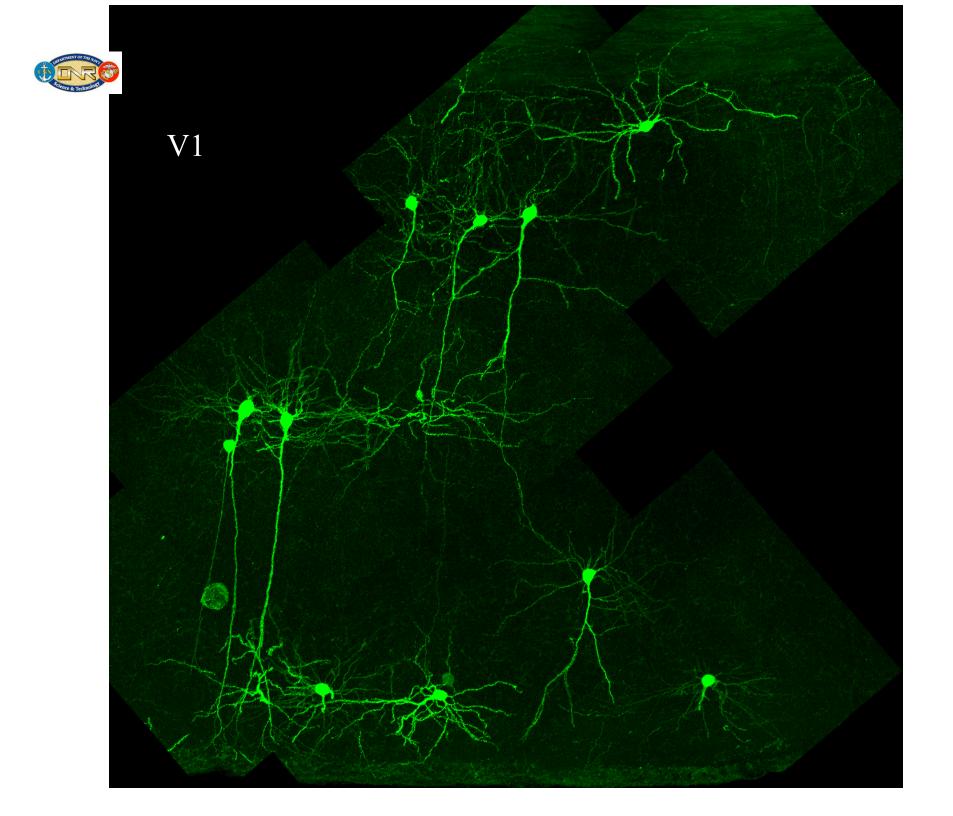

# **NEUROMORPHIC ENGINEERING**

Bionics-implanted devices with hybrid digital-analog computing

**Bionic ear (cochlear)**

**Bionic eye (retina)**

Monitoring brain functions (control of epileptic seizures)

Wireless

Nano-power (Low power battery with wireless recharging)

**Material compatibility**

**Energy harvesting**

Largest Obstacles:

Connection to neuronal networks Determining and replicating cortical neuronal networks Analysis of action potentials of neuronal systems

### NANOELECTRONICS AND NEW ARCHITECTURES

# WHO PAYS?

LOOK FOR NEW APPLICATIONS!

CELLULAR NONLINEAR/NEURAL NETWORKS

**MAGNETIC COMPUTER**

**BIO-IMPLANTED PROSTHESES**

TAKE ADVANTAGE OF SPECIAL PROPERTIES OF THE NEW DEVICES REJECT THE DEVICES WHICH DON'T MEET THE CHALLENGES

Sci. Am. May 2009

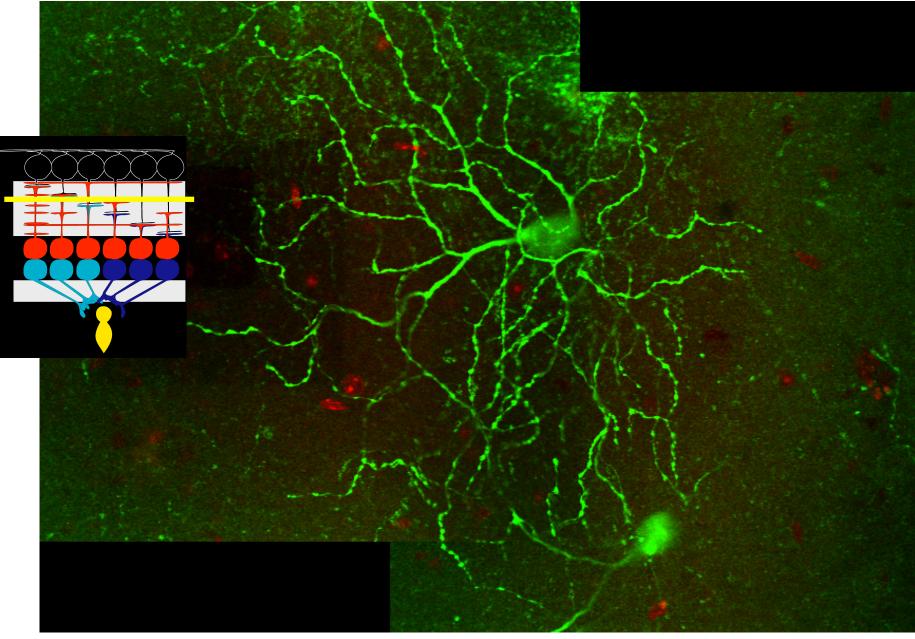

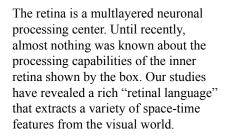

### Deriving the Algorithms from the Physiology

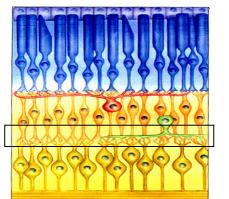

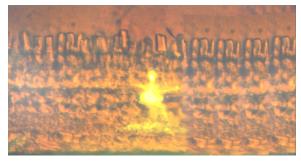

Here's an example of a living slice of retina resembling the textbook illustration above But all cells are alive and can be studied.

The inner retina is comprised of more than a dozen strata. Each stratum carries a unique representation f the visual world These representations can be "read out" by recording electrodes

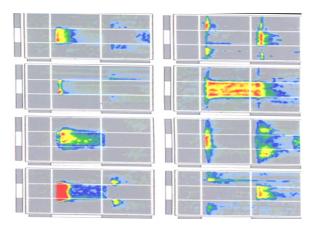

This is a set of 4 of more than a dozen space-time representations derived from electrode measurements Each representation in the inner retina, is carried to the brain by a separate ganglion cell type reading from a separate stratum (above). These represent a full "feature set" of space-time filters that completely characterize the visual world for us.

# InAs/AISb/GaSb The All-Purpose Electronics Material

**Lattice Matched Heterojunctions**

**RTD and RITD-Resonant tunneling devices**

DSP (>TeraHertz)

SRAM

**Dilute Magnetic Semiconductor**

**Optical detector**

Infra-red detectors (2-13 micron wavelengths)

TeraHertz detector for imaging systems

Low power high frequency heterojunction transistor

Nanowire transistors and diodes

Hybrid devices

**Multi-value logic**

**Multi-state memory**